플립플롭

플립플롭 또는 래치(영어: flip-flop 또는 latch)는 전자공학에서 1 비트의 정보를 보관, 유지할 수 있는 회로이며 순차 회로의 기본요소이다. 조합논리회로에 비해 플립플롭은 이전상태를 계속 유지하여 저장한다. 디지털 공학에서 입력을 출력에 반영하는 시점을 클럭 신호의 순간 엣지에서 반영하는 플립플롭과, 입력에 따라 항상 반영되는 래치로 구분된다. 필요한 플립플롭의 클럭 신호는 수정 발진기 등을 이용하여 생성한다. 복잡한 회로는 많은 플립플롭이 같은 클럭신호를 사용하므로 전용의 클럭 배선이 필요한 경우도 있다. 래치는 입력되는 순간 바로 반영하기 때문에 플립플롭처럼 엣지의 시점을 결정하는 논리회로가 없어도 되므로 래치의 논리회로가 간단하다.

디지털 시스템 설계에서의 회로를 구성할 때, 조합논리와 결합하여 순차회로의 기능을 구현하는 중요한 요소이다. 마이크로프로세서와 같은 디지털 로직을 사용하는 많은 전자회로에 사용한다. 시계의 카운터회로나 기타 복잡한 디지털 회로에는 필수적 요소이다.

조합 회로를 단순하게 조합 논리 기능을 실현하는 회로가 아니고, 지연된 하나의 출력을 피드백하여 입력에 넣으므로써 정보를 보관, 유지하는데 사용하는 특징이 있다. 조합 회로에서 일반적으로 출력의 반대 논리인 음의 성질로 여겨지는 출력 신호의 지연을 피드백, 루프의 입력 신호에 사용하도록 구성하는 것이 흥미롭다.

플립플롭과 래치는 구조상 휘발성이다. 즉 정보는 전원이 있을 때만 보관, 유지되며 전원이 차단되면 정보는 사라진다. 처음 전원이 인가되면 입력이 인가되지 않은 상태에서 Q의 출력 상태가 결정되어야 한다. 이것은 되먹임 회로에서 출력과 입력간의 경쟁 상태로 인해 임의로 결정된다. 회로 설계자 입장에서는 초기 Q의 상태를 예측할 수가 없다. 따라서 초기의 상태를 결정하기 위해 입력 신호 외에 별도의 비동기 신호인 SET(Q을 H로)과 RESET(Q을 L로) 신호를 추가하는 경우도 있다. 이 경우 플립플럽은 비동기로 Q의 신호가 결정되고 이 신호가 액티브 되면 클럭과 입력은 무시되는 최우선 신호이다. S-R 래치 기능과 유사하다.

디지털 회로에서 각종 카운터나 상태제어 등에 필요한 요소이다. 이전의 상태를 계속 유지하는 상황이 되면 플립플롭 또는 래치를 사용한다. 플립플럽은 클럭 신호가 필요하며, 클럭의 순간적인 상태변화(엣지) 시점에서 입력이 출력에 반영된다. 여러 개의 플립플럽으로 회로를 구성할 경우, 각 플립플럽의 클럭입력을 같은 클럭신호를 사용하여 같은 시간에 변화하는 것을 동기 회로라 한다. 경우에 따라 각 플립플럽의 클럭이 따로 입력하는 비동기 회로도 있고, 공통 클럭 뿐만 아니라 다른 출력을 클럭으로 사용한다.

컴퓨터의 주기억장치나 CPU 캐시, 레지스터를 이루는 기본 회로 가운데 하나이다. 그 구조는 계전기 (릴레이)를 이용한 자기 보관유지 회로 (셀프홀드 회로)에도 비슷하게 사용되고 있다. 플립플롭으로

플립플롭은 내부가 논리 회로로 구성되어 있기 때문에 논리 회로에 준하는 빠른 동작속도를 얻을 수 있다. 예를 들어 컴퓨터의 기억장치를 구성하는 회로에서 주로 사용되는 방식인 디램 (DRAM)의 기억 소자와 비교했을 때 기억내용의 변경에서 축전기 (캐패시터라고도 함) 충전/방전을 기다릴 필요가 없고 기억내용의 읽기에서 내용에 영향을 주지 않아서 비파괴 읽기이며 정기적인 리프레시 동작도 필요하지 않는다. 반면에 1 비트의 회로가 복잡하기 때문에 대규모가 되면 1 비트당 비용이 비싸지는 경향이 있다. 이러한 성질 때문에 최근에는 플립플롭을 CPU 캐시나 중앙 처리 장치의 레지스터같은 비교적 소용량으로 고속성이 요구되는 곳에 사용하고 주기억에는 주로 디램을 이용하는 것처럼 기억 계층을 구성해서 다른 회로방식의 기억장치와 조합한 형태로 사용되는 것이 많다.

플립플롭 종류

[편집]래치(latch)

[편집]래치는 한 비트의 정보를 데이터가 바뀌기 전까지 계속 유지하는 회로이다. 따라서 출력 Q을 0 또는 1로 상태전이가 필요하다. 래치 종류에 따라 입력은 한 개 또는 두 개를 사용한다.

논리 회로 시스템 설계에서 경우에 따라 래치의 입력을 반영할 시점을 조절할 필요가 있다. 즉, 입력 신호가 들어와도 입력 시기를 조절하여 Q의 상태변화가 없도록 하는 제어 신호가 있고, 이것으로 입력을 무시하거나 또는 출력에 반영할 수 있다. 이때 사용하는 신호가 게이트(gate, 또는 enable)이다. 표시는 E(enable, E, EN, G 등으로 표시)로 하고, 입력신호와 별도의 제어 입력이 같이 있다. 이 신호가 존재하는 래치를 게이트-래치(gated latch)라고 한다.

E 신호가 없을 경우는 입력의 상태가 바로 반영된다.

| E신호가 없는 경우 | E신호가 있는 경우 |

|---|---|

|

|

Q의 상태변화를 위해, 입력 중 어떤 S-R입력은 상태변화를 유도하고 어떤 입력은 이전의 상태가 계속 유지된다.

|

EN 신호가 액티브 되었을 때, 입력이 반영된다. 이 신호가 액티브 되면 입력이 계속 반영된다. 클럭의 엣지와는 다르다. 내부에 AND와 같은 게이트로 입력되는 시점을 제어한다.

|

래치는 G(EN) 입력 값이 1일 때 입력된 데이터를 출력한다. G신호가 계속 1이면 입력 신호가 그대로 출력 신호로 나온다.

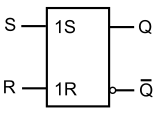

간단한 set-reset 래치

[편집]SR NOR 래치

[편집]

SR 래치는 가장 간단한 순차회로이다. 여기서 S(set)는 출력 1을, R(reset)은 출력 0으로 되도록 한다는 의미이다. NOR 논리 게이트를 교차 되먹임 입력을 통해 만들어진다. 저장된 현재 상태출력은 Q로 표시한다.

S과 R 입력이 모두 0이면, Q와 Q 출력 상태가 되먹임(feedback) 입력되어 이전상태가 유지된다. 만약 S (Set)가 H이고, R (Reset)이 L이면, 출력 Q는 H로 된다. 만약 R이 H이고 S가 L로 입력되면, 출력 Q는 L 상태가 된다.

| SR 래치 동작[1] | ||||||||

|---|---|---|---|---|---|---|---|---|

| 특성표 | 여기표 | |||||||

| S | R | Qnext | 동작 | Q | Qnext | S | R | |

| 0 | 0 | Q | 상태유지 | 0 | 0 | 0 | X | |

| 0 | 1 | 0 | reset | 0 | 1 | 1 | 0 | |

| 1 | 0 | 1 | set | 1 | 0 | 0 | 1 | |

| 1 | 1 | X | 부정(사용불가) | 1 | 1 | X | 0 | |

SR NAND 래치

[편집]

NAND 논리 게이트로 구성된 간단한 SR 래치도 있다. Set과 reset가 L 입력에 의해 액티브 되고, S과 R로 나타낸다. SR 래치는 입력 L에서 활성화(active-low) 된다.

|

| ||||||||||||||||||||||||||||

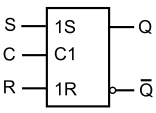

게이트 신호에 의한 조건 천이 래치

[편집]래치에서 게이트 신호(E, EN, G)는 입력을 출력에 반영할것인가를 결정하는 조건 입력이다. 따라서 게이트가 켜짐(active)되어야 입력이 출력에 반영된다.

SR NOR 래치

[편집]게이트 SR 래치

[편집]

SR 입력신호를 선택적으로 무시할 수 있도록 단순 SR래치 앞에 AND 게이트를 붙여 놓은 형태로 게이트 SR 래치를 구성할 수 있다. 게이트 신호 E가 enable되지 않으면 입력신호를 무시해야 하므로, 이전 상태가 유지되는 뒤단의 단순 래치의 입력에 SR=00가 되도록 하면된다.

- E=H(high, enable 참) : 뒤단의 래치 입력 SR=(0,0)=유지되고, S와 R 중 하나가 H가 되면 상태전 된다.

- E=L(low, enable 거짓) : AND 로직에 의해 뒤단의 래치 입력 SR=(0,0)=유지가 되어 상태천이가 없다.

여기서 게이트 enable 신호는 종종 클럭 신호를 사용하고 클럭 펄스가 H일 때 SR 입력신호가 반영된다. 그러나 동기식 플립플럽의 엣지에서만 동작하는 것과 차이가 있다.

|

|

게이트 D 래치

[편집]

D 래치는 SR의 상태천이를 유도하는 SR 입력이 01 또는 10 만이 존재한다. SR 래치의 입력 SR=11과 SR 래치의 입력 SR=00은 Q와 Q 출력이 같은 상태가 된다. 기본적으로 플립플럽에서 Q와 Q 출력이 상반된 상태가 나와야 한다. 따라서 Q와 Q 출력이 같은 논리는 피해야 한다. D 래치는 입력이 하나이므로 SR 래치의 금지된 상태가 되지 않도록 S와 R이 항상 반대의 로직이 되도록 D 입력의 NOT 게이트를 사용 하면된다.

게이트 D 래치(gated D latch)는 단순 D 래치에 D 입력 신호를 무시하도록 AND을 붙여 뒤단의 상태가 상태유지가 되도록 조절하면 된다. 따라서 뒤단의 SR 입력이 SR=00 또는 SR=11이 되면 상태천이 없이 유지된다.

논리회로를 구현하는 집적회로에서 칩당 여러 개의 논리게이트를 넣어 만든다. 7400계열에서는 74HC75가 4개의 D 래치가 존재한다.

|

|

진리표에서 enable/clock 입력이 0이면 D 입력신호는 무시되고, H이면 D 입력이 반영되어 출력이 D와 같게 된다.

JK 래치

[편집]JK 래치는 다음과 같은 상태표를 갖는다:

| JK 래치 진리표 | ||||

| J | K | Qnext | Comment | |

| 0 | 0 | Q | 상태 유지 | |

| 0 | 1 | 0 | Reset | |

| 1 | 0 | 1 | Set | |

| 1 | 1 | Q | 토글(Toggle) | |

게이트 신호가 있는 것과 없는 것의 차이

[편집]D 플립플럽

[편집]

D 플립플럽(flip-flop)은 광범위하게 사용한다. D는 데이터(data) 또는 delay로 알려져 있다.

D 플립플럽은 입력 D의 값을 클럭의 엣지(edge)에서 캡처해서 Q에 반영한다. 엣지가 발생하지 않는 시간에는 Q가 변하지 않고 유지한다.[2]

D 플립플럽 진리표:

Clock D Qnext 상승 엣지(Rising edge) 0 0 상승 엣지(Rising edge) 1 1 엣지 없음 X Q

('X'표시는 Don't care 조건을 말한다. H와 L 어느 것이든 상관이 없다는 뜻이다.

D 플립플럽의 동기를 위한 클럭신호는 상승엣지와 하강엣지를 사용한다. 심볼에서 > 앞에 동그라미를 붙이면 하강엣지를 사용하고 있다는 뜻이다.

D 플립플럽의 SR 입력은 비동기 입력으로 Set과 Reset 기능이다. 이 입력이 액티브되면 입력 D와 C는 무시된다.

D 플립플럽의 출력 상태 변화는 클럭의 엣지에서만 이루어지는데, 필요에 따라 비동기로 임의의 시간에 Q을 1 또는 0으로 만들 때 S 또는 R 신호를 이용한다. 이것은 마지막 단에 S-R 래치와 같이 동작하도록 설계한다. 따라서 SR 래치처럼 입력을 제어해야 한다.

S=R=0 일 경우, 입력 D와 C에 의해 상태변화가 되고, S 또는 R이 하나만 1일 때 비동기로 즉각 Q의 상태변화가 일어난다. SR=11이면 출력 QQ=11이므로 사용하지 않는다.

Inputs Outputs S R D > Q Q' 0 1 X X 0 1 1 0 X X 1 0 1 1 X X 1 1

T 플립플럽

[편집]

입력 T=H 이면, Q의 출력이 반대 논리로 전이된다. 입력 T=L 이면, Q의 출력은 상태천이 없이 유지된다. T(toggles)는 상태가 반전되는 것을 말한다.

이 동작을 특성방정식으로 나타내면:

- (XOR 동작의 확장)

T 플립플럽 진리표:

| T 플럽플럽 동작[3] | ||||||||

|---|---|---|---|---|---|---|---|---|

| 특성표 | 여기표 | |||||||

| 기능 | 동작 | |||||||

| 0 | 0 | 0 | 홀딩 상태 | 0 | 0 | 0 | 상태유지 | |

| 0 | 1 | 1 | 홀딩 상태 | 1 | 1 | 0 | 상태유지 | |

| 1 | 0 | 1 | 토글 | 0 | 1 | 1 | 반대 천이 | |

| 1 | 1 | 0 | 토글 | 1 | 0 | 1 | 반대 천이 | |

T=H가 계속 유지되면 클럭 신호의 주기가 2배 늘어나고, 주파수는 1/2로 된다.

JK 플립플럽

[편집]

JK 플립플럽은 RS 래치에서 금지된 입력(RS 래치에서 RS='11')을 토글로 바꾸어 동작하도록 만들어진 플립플럽이다. 결국 RS 플립플럽에 토글 기능을 합친 플립플럽이다.

입력 JK가 논리 입력 00, 01, 10은 RS 플립플럽과 같고, JK=11일 때, Q는 반전된다.

이 기능을 특성방정식으로 표현하면:

JK 플립플럽 진리표는:

|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

플립플롭과 표준 논리 IC

[편집]RS형을 제외하고 표준 논리 IC로 제공되고 있다. (RS형은 구조가 간단하고 NAND 게이트 2개로 구성이 가능하므로 NAND 표준 논리 IC를 사용하면 충분하기 때문임) 또한 핀 수가 4개에서 6개 정도이므로 1개의 논리 IC에 2개 이상을 포함되어 있는 것이 대부분이다.

참조

[편집]- ↑ Roth, Charles H. Jr. "Latches and Flip-Flops." Fundamentals of Logic Design. Boston: PWS, 1995. Print.

- ↑ “Edge-Triggered Flip-flops”. 2013년 9월 8일에 원본 문서에서 보존된 문서. 2013년 9월 16일에 확인함.

- ↑ 가 나 Mano, M. Morris; Kime, Charles R. (2004). 《Logic and Computer Design Fundamentals, 3rd Edition》. Upper Saddle River, NJ, USA: Pearson Education International. pg283쪽. ISBN 0-13-191165-1.